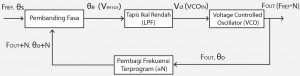

Phase-Locked Loop (PLL) adalah sebuah blok fungsi yang dapat digunakan untuk menghasilkan clock berdasarkan referensi juga dari sebuah clock. PLL memiliki kelebihan dibandingkan osilator pada umumnya. Sesuai dengan namanya, bahwa mekanisme di dalam sistem PLL akan berusaha untuk selalu mengunci relasi antara gelombang referensi dengan gelombang keluaran yang dihasilkan. Sifat “mengunci” menyebabkan sebarang sumber frekuensi memiliki ketelitian tinggi, misalnya 1 ppm (0,1%), dengan PLL dapat dihasilkan sebarang frekuensi keluaran dengan ketelitian 1 ppm tadi. Sistem PLL tersusun atas 4 blok utama yaitu blok pembanding fasa, tapis ikal rendah, osilator terkendali tegangan dan pembagi frekuensi terprogram.

Dasar Phase-Locked Loop (PLL)

Hasil dari mekanisme ikal tertutup ini adalah tercapainya kondisi “locked” yaitu kondisi fasa dan frekuensi clock keluaran sama persis dengan fasa dan frekuensi clock masukan. Kesamaan fasa keduanya dijaga tetap terkunci sehingga memiliki ketelitian tinggi dan sistem akan stabil. Adanya blok pembagi frekuensi yang berfungsi membagi frekuensi keluaran dengan faktor pembagi berupa suatu konstanta sebesar (N), maka frekuensi keluaran (FOUT) sistem PLL dirumuskan sesuai persamaan berikut :

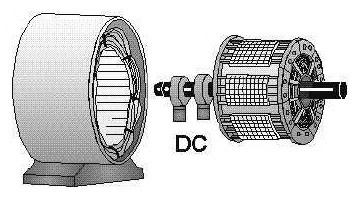

Prinsip Kerja Operasi PLL Motor DC

Secara umum konsep kendali kecepatan motor DC menggunakan pola ikal tertutup sesuai gambar berikut.

Pengendalian Kecepatan Motor DC Menggunakan Referensi Kecepatan

Pada gambar diatas, kecepatan aktual rotor akan selalu menyesuaikan dengan besar kecepatan referensi. Apabila blok sensor kecepatan menggunakan suatu roda tacho (optical encoder) maka kecepatan aktual motor dinyatakan dalam suatu serial pulsa (clock). Setiap 1 Hz clock akan setara dengan kecepatan aktual (1/H) rps, dimana H adalah jumlah lubang roda tacho. Dengan demikian maka kendali kecepatan motor DC dapat dilakukan menggunakan referensi berupa suatu clock, sesuai gambar berikut.

Pengendalian Kecepatan Motor DC Menggunakan Referensi Clock

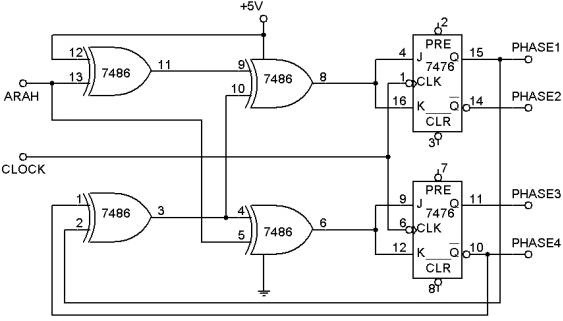

Prinsip operasi gambar pengendalian kecepatan motor DC menggunakan referensi clock identik dengan gambar pengendalian kecepatan motor DC menggunakan referensi kecepatan. Blok penguat selisih menggunakan suatu rangkaian

pembanding fasa. Rangkaian pembanding fasa berfungsi membandingkan parameter fasa dari clock referensi terhadap fasa clock kecepatan aktual rotor. Blok controller menggunakan suatu rangkaian tapis ikal rendah (LPF).

Konsep dasar gambar pengendalian kecepatan motor DC menggunakan referensi clock dimodifikasi dengan implementasi konsep elektronika daya dan konsep PLL ke dalam sistem. Keseluruhan sistem tersusun dari dua blok utama yaitu blok rangkaian master dan blok rangkaian slave.

Diagram Blok Kendali Kecepatan Motor DC Menggunakan PLL

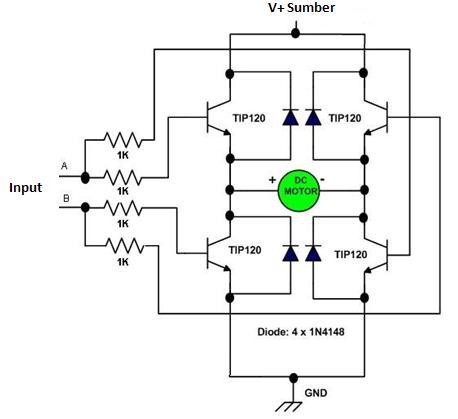

Blok penggerak motor DC tersusun dari blok modulasi lebar pulsa (PWM) dan blok rangkaian daya yang dapat berupa DC Chopper atau Half Bridge Converter. Dasar sistem pengendalian motor DC mengacu pada persamaan berikut:

Saat tercapai kondisi terkunci (locked) maka clock umpan balik akan memiliki fase dan frekuensi yang sama dengan clock referensi. Blok tapis ikal rendah (LPF) memiliki peran penting karena menentukan waktu tanggapan sistem PLL mencapai kestabilan (lock time). Idealnya respon sistem dirancang berosilasi sesaat (teredam kritis).

Buat Pesan Untuk Artikel "Definisi Dan Prinsip Kerja Phase-Locked Loop (PLL) Pada Motor DC"